研究計劃1 - 突破硬件瓶頸的新興技術

研究計劃1針對存儲和數據帶寬問題,探索和集成矽兼容的新興技術和不斷演進的傳統矽晶片技術,從而緩解 AI 硬件所面臨的瓶頸。

研究項目1-1:

用於類腦計算(Neuromorphic)的基於可變電阻式存儲器(ReRAM)的電路

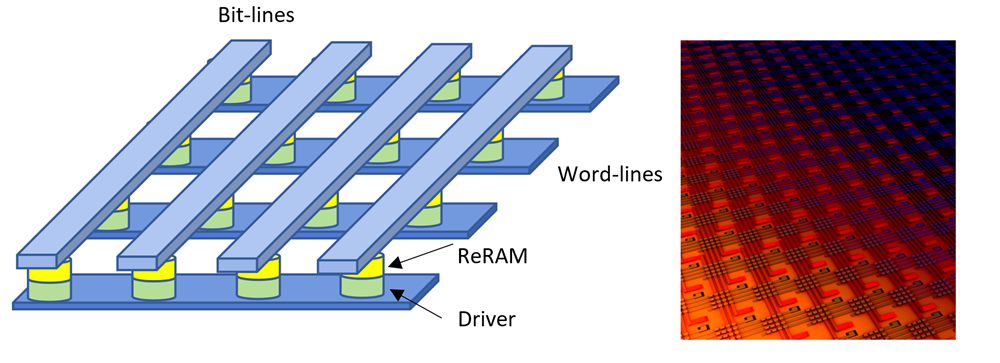

圖 研究項目1-1: 包括驅動的基於 ReRAM 的交叉開關矩陣結構

研究項目1-1 涵蓋了 3D 集成晶片的開發,包括可變電阻式存儲器( ReRAM) 和基於CMOS 的處理器,用於實現高能效的向量-矩陣乘法運算部件。 研究項目1-1 的目標還包括探索速度、密度、面積、能耗、變化和頑健性之間的權衡優化,研究高密度非易失性存儲器 ReRAM 對不同目標領域的 AI 晶片和系統的適用性和最佳應用方法。

研究項目1-2:

用於具有高連接性的 AI晶片的 3D 技術

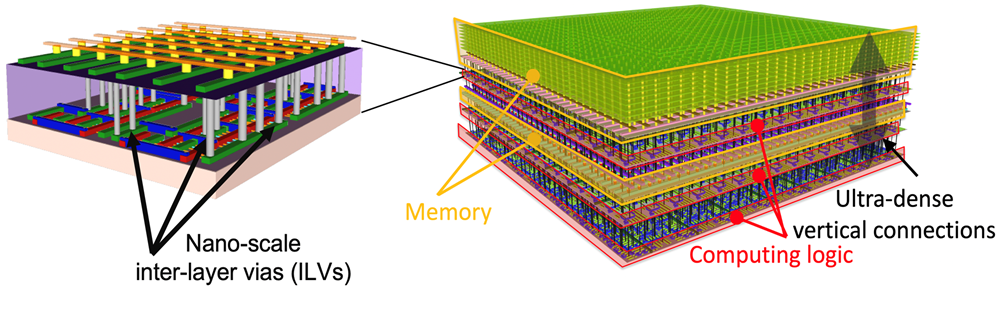

圖 研究項目RP1-2: 通過垂直堆叠的存內計算系統示例

研究項目1-2 解决類腦計算(Neuromorphic)中海量計算與存儲單元之間的互連需求。由於寄生電阻和電容的存在,目前基於片外存儲器的主流方法已成爲速度和功耗/能耗的主要瓶頸。包括 2.5D/3D 和單片集成在內的3D 集成技術,通過在物理空間中提供額外的維度來連接不同的電路元件,從而解决上述互連問題。該方法具有更高帶寬和更低延遲的優勢,從而使系統的能量-延遲乘積降低了 1,000 倍以上,並且晶片外形更小、電路塊耦合更緊密。

研究項目1-3:

用於人工智能系統的高性能矽基光子(Silicon Photonic)技術

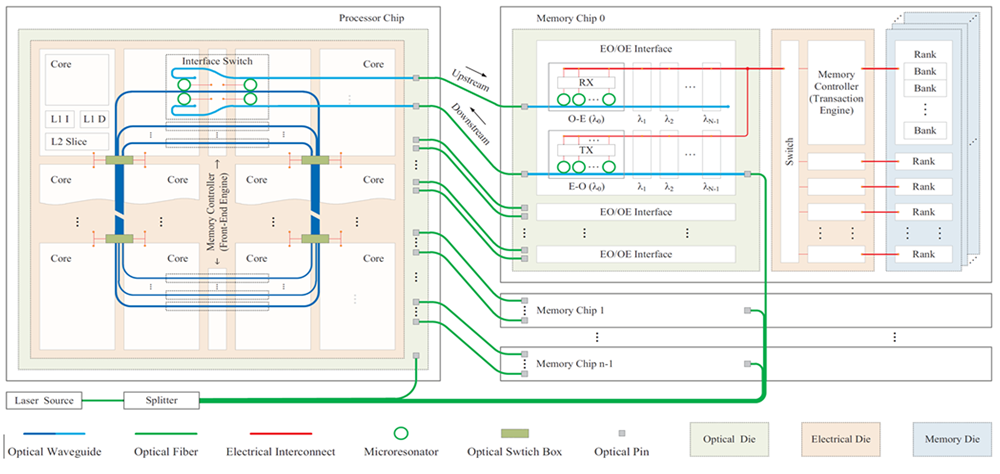

圖 研究項目1-3: 用於人工智能系統的矽基光子存儲網絡

傳統的計算系統基於 CMOS 技術,隨著摩爾定律走向終結, AI 應用對於計算能力的需求不斷增長,帶來成本和能耗持續而顯著的增加。與 CMOS技術相比,矽基光子(Silicon Photonic)技術的進步有望實現更高的能效、超高速和低延遲。矽基光子技術爲人工智能架構、電路和工具開闢了新的機會,通過全面探索新方法來應對後摩爾定律時代AI系統所面臨的挑戰。

研究項目1-4:

從技術到類腦計算(Neuromorphic)的器件建模

圖 研究項目1-4: 從物理緊凑模型到更高級別的 EDA 工具和應用程序設計

緊凑模型(Compact Model)是新興半導體器件到應用之間的重要橋梁。目前EDA 工具中使用傳統的准靜態設備建模方法,難以處理動態存儲設備和基於脉衝信號(spike)的類腦計算(Neuromorphic)系統。 研究項目1-4 專注於動態變化建模方法,以解决 EDA 工具中的存儲仿真問題。除了電流-電壓域之外,項目研發的緊凑模型也將能夠進行時域中的詳細仿真。