研究计划3 - 大规模人工智能硬件的电子设计自动化(EDA)

探索人工智能芯片与系统设计EDA的新前沿,聚焦于支持芯粒(Chiplet)及3DIC设计,突破现有EDA工具的技术瓶颈及开发基础AI模型在各种设计任务中的应用,以实现更灵活的芯片设计。

研究項目3-1:

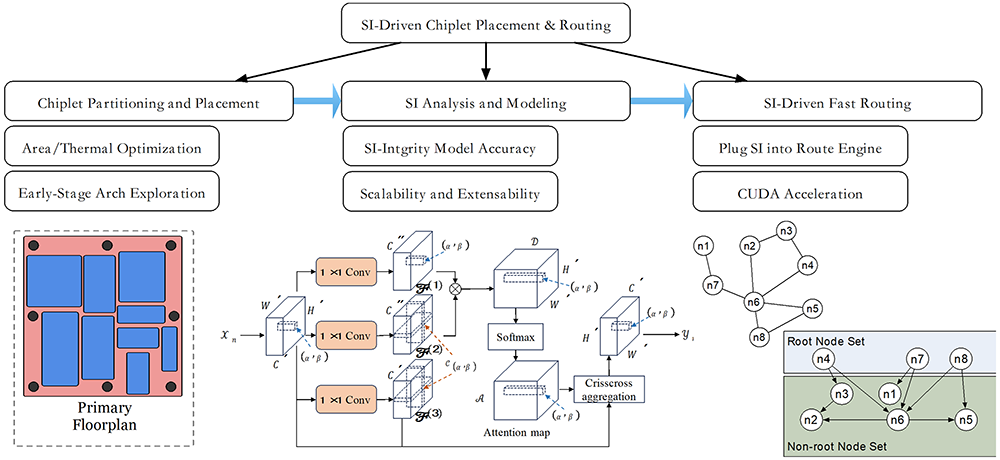

面向芯粒(Chiplet) 的人工智能芯片信号完整性驱动的电子设计自动化

研究项目3-1旨在研发面向基于芯粒(2.5D封装)设计的自动化(EDA)解决方案,特别优化大规模 芯粒设计中的信号完整性(Signal Integrity, SI)问题。项目将首先支持自动化的芯粒分割与布局规划,综合优化芯片面积、功耗等多重设计目标;同时,通过深入研究硅基板的互连结构与拓扑特性,构建具备可扩展性与高效率的信号完整性分析方法。在此基础上,开发一套以信号完整性为驱动的快速布线优化工具。

研究項目3-2:

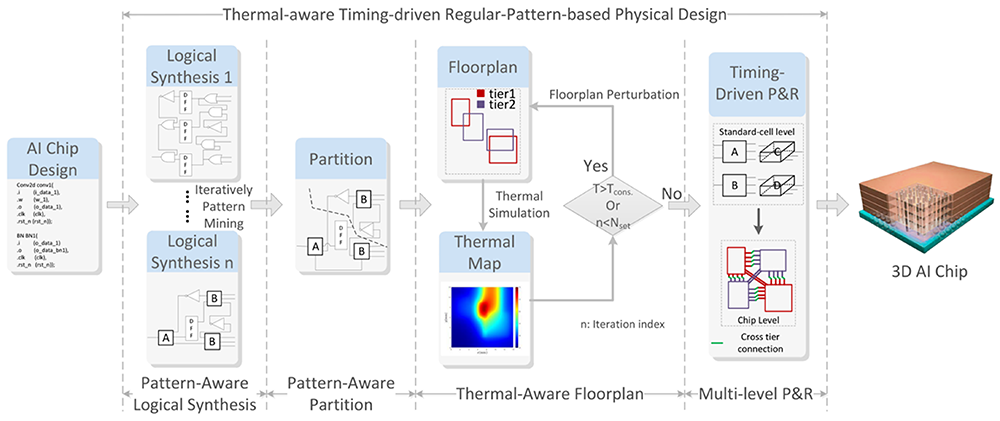

面向模式感知和热感知的3D人工智能芯片电子设计自动化

研究项目3-2将进一步支持基于3D集成电路(3D IC)架构的人工智能芯片设计。该技术透过硅通孔(TSV)实现多个芯粒的垂直堆叠,显著提升存储带宽与系统集成度。本研究提出针对3D IC导向的模式感知和热感知电子设计自动化(EDA)解决方案,研究团队将利用人工智能芯片中处理单元(PE)的规则性特征,加速整体 3D人工智能芯片的物理设计流程。此外,项目将开发专用的热仿真器,实现芯片堆叠式 3D IC 的快速且精确的热力分析;并在此基础上构建具备热感知能力的3D布局规划工具,以优化 3D IC 的设计与执行效率。

研究項目3-3:

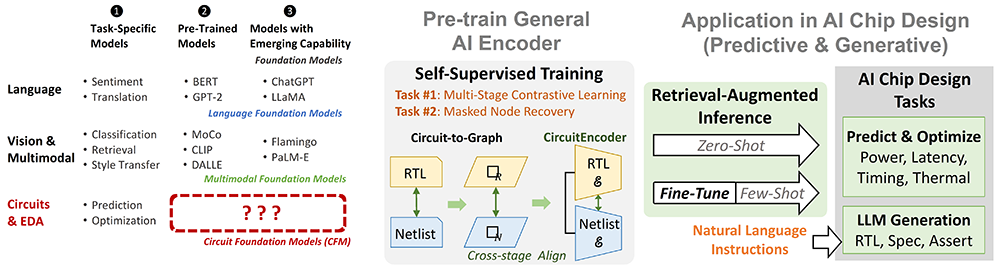

基于AI基础模型的人工智能芯片靈活设计方法

研究项目3-3旨在基于定制化的AI基础模型,开发先进的人工智能辅助电子设计自动化(EDA)技术。研究团队将预训练通用电路编码器,以生成每个电路组件的表征。该通用电路表征方法可实现从 RTL 级到布局阶段的跨层设计一致性,并支持多种差异化的下游应用场景。基于包含丰富电路信息的特征表示,项目将构建各种人工智能模型,用于对延迟、时序与能效等关键设计指标进行早期、快速且精细的评估。此外,项目还将开发生成式人工智能模型,以辅助人工智能芯片的靈活自动化设计与优化。