RP3 - EDA (Electronic Design Automation) for Large-Scale AI Hardware

Exploring new frontiers in EDA for AI chip and system design, with the primary focus placed on supporting the chiplet- and 3DIC-based designs, overcoming the limitations of existing EDA tools, and exploring the employment of foundation AI models in various design tasks to enable more agile chip design.

RP3-1:

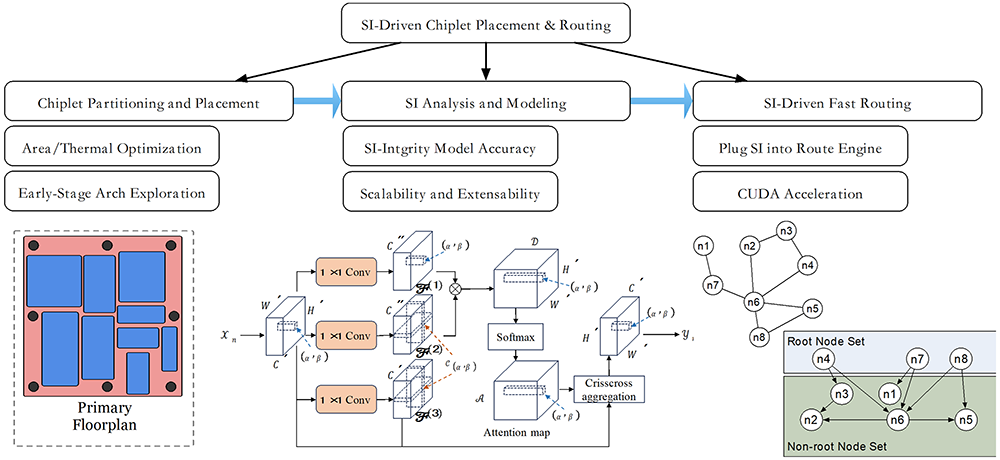

Signal Integrity-Driven EDA for Chiplet-based AI Chip

This project will develop EDA solutions for chiplet-based (i.e., 2.5D) AI chip designs, especially optimizing the signal integrity problem in large-scale chiplet designs. It will first support automated chiplet partitioning and floor-planning, optimizing multiple design objectives, such as area and power. Moreover, this project will develop scalable and efficient signal integrity (SI) analysis methods by studying the interconnection structure and topological characteristics of the silicon substrate. Based on the signal integrity analysis method, a set of signal integrity-driven fast routing optimization tools will be delivered.

RP3-2:

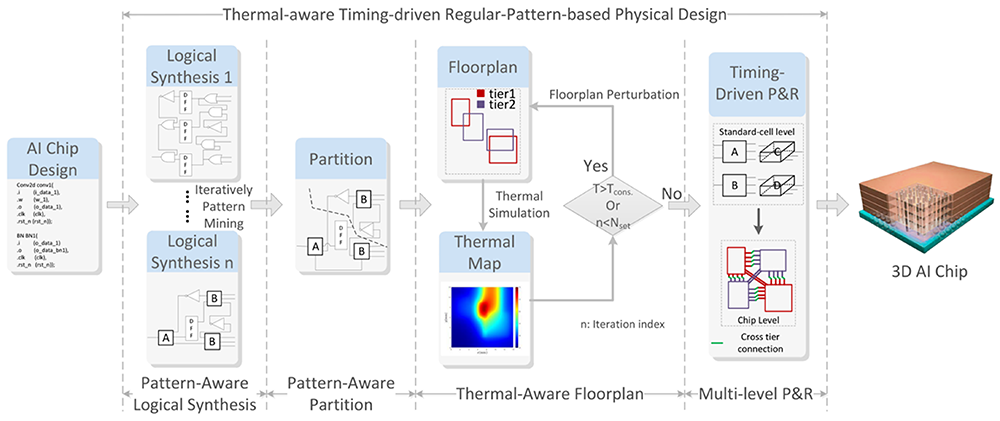

Pattern- and Thermal-Aware EDA for 3D AI Chip

This Project will further support AI chips based on 3D ICs, which vertically stack multiple chiplets via through-silicon via (TSV) to significantly enhance memory bandwidth. PR3-2 proposes pattern- and thermal-aware EDA solutions for 3D IC. The Team will leverage the regularity of PEs in AI chips to speed up the whole physical design process of 3D AI chips. Moreover, they will develop a thermal simulator for fast and accurate thermal estimations of chip-stacked 3D ICs. Based on the thermal simulator, a 3D thermal-aware floorplanner will be developed to optimize the 3D IC implementation.

RP3-3:

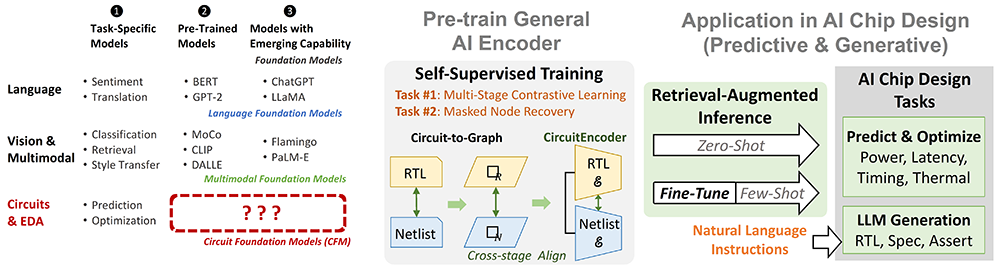

Agile AI Chip Design Methodology based on Foundation AI Models

This Project will develop cutting-edge AI-assisted EDA techniques based on customized foundation AI models. They will first pre-train general circuit encoders that can generate a representation for each circuit element. The general circuit representation will be aligned across design stages from RTL to layout, and support largely distinct downstream applications. Based on representations with rich circuit information, various AI models will be developed for early, fast, and fine-grained evaluation of primary design qualities, including latency, timing, and power. Moreover, generative AI models will be developed to assist the generation of AI chip design.