Sections

Left Column

Right Column

Text Area

Ai-DTCO and Specialty IP

Text Area

背景介紹

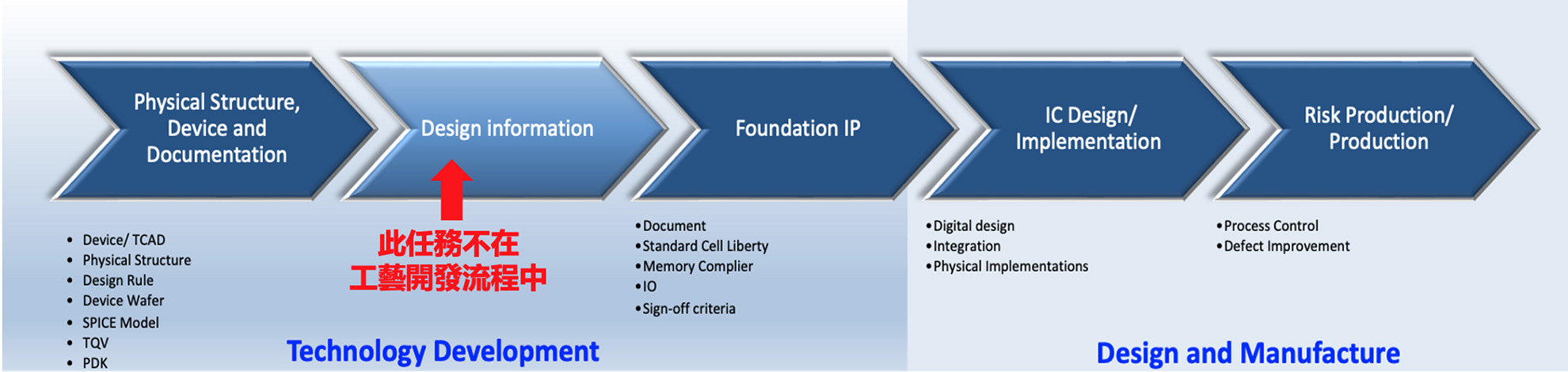

積體電路製造技術持續演進,數十年間來元件特徵尺寸縮小了近千倍(10-6 m至10-9 m)。結構已從平面型( Plannar )、鰭型(FINFET)到環閘(GAA)型態。製造流程及設計規則更從幾十道迅速增加到幾千道。晶片規模也從幾千個增加到數十億甚至數百億個電晶體。為了適應龐大的晶片設計和複雜的技術及製造過程如何更好配合(Design Technology Co-optimization DTCO),以最小面積功耗發揮最大效用是積體電路設計生產公司的一大痛點。本技術基於人工智能,協同分析電路和製程技術的特徵,並以人工智能自動生成最適合電路設計和技術的基礎IP,為積體電路行業提供最佳的DTCO解決方案,並進一步提供誇越高技術門檻、高可靠性及超低功耗應用等障礙所需的特殊IP。

Text Area

創新亮點

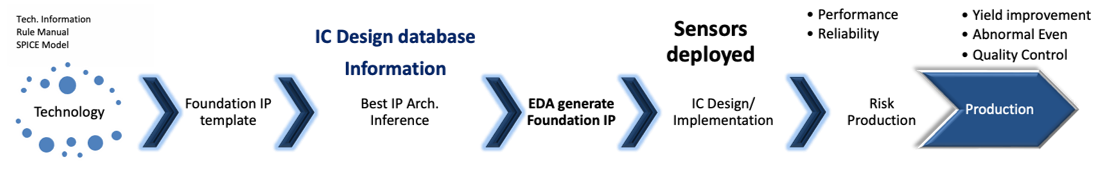

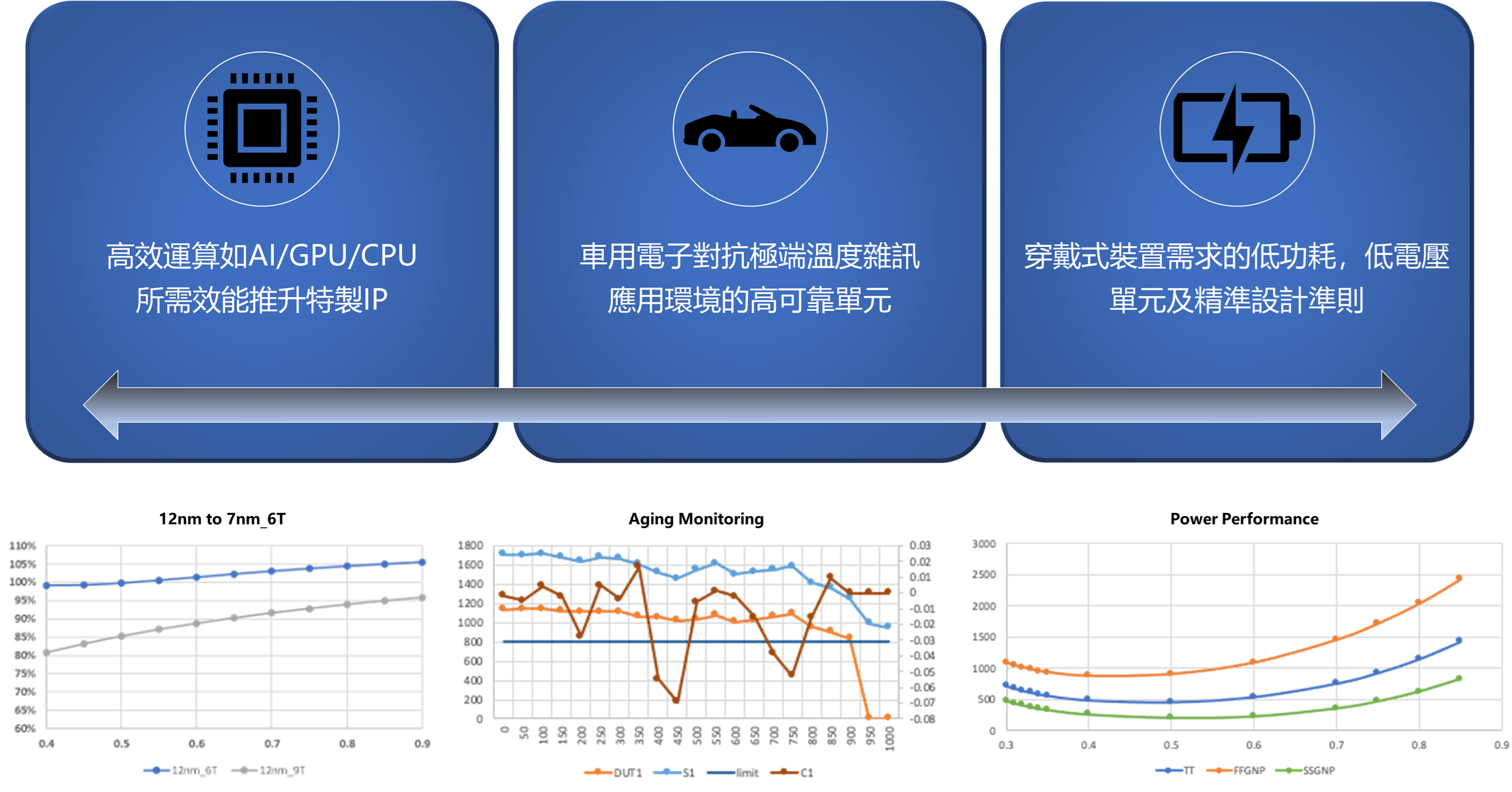

本技術以人工智能為基礎,在工藝開發階段即可導入晶片設計資料,協同分析電路及工藝技術的特性,並以人工智能自動生成最能契合電路設計及工藝的基礎IP協助積體電路設計最適切的揉和製造工藝,並進一步提供跨越高技術門檻如高效運算,高可靠度及超低功耗所需特用基礎IP。

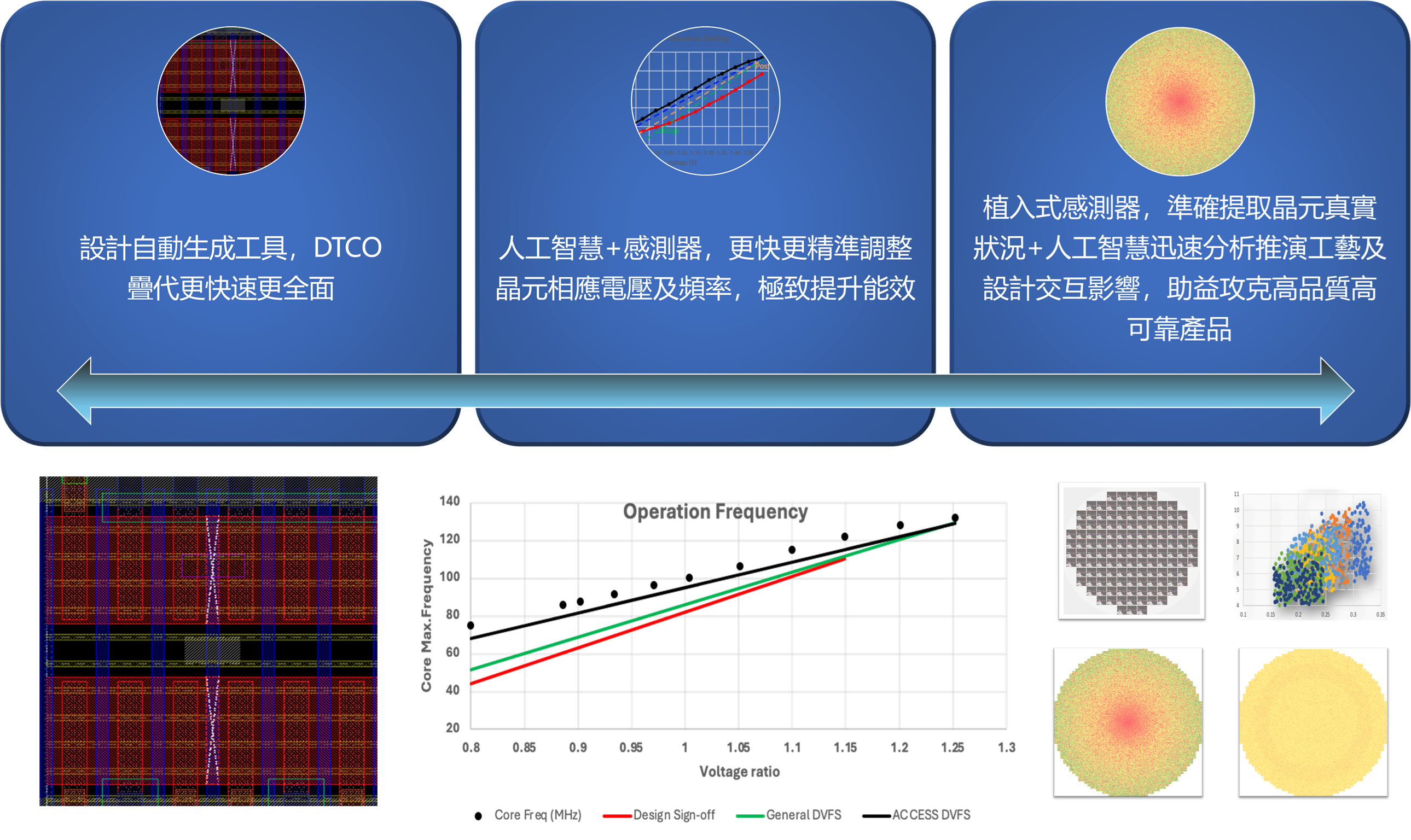

除了以人工智能揉和製造工藝和積體電路設計自動化生成適用於一般應用,高效運算,高可靠度及超低功耗所需基礎IP外,本項目更致力於解決工藝流程在生產過程各道環節偏移逐步累積的誤差導致元件電氣特性飄移(Variation)現象,以嵌入晶片中的各類感應器,量測積體電路製造成品的電路特性,及積體電路設計遺留的各類現象,輔以人工智能為基底的分析工具,協助工程師監控判斷問題,提供進一步優化設計,改進工藝,品質管控的依據。

Text Area

效能優化

Text Area

積體電路健康狀態

Text Area

如對我們的技術感興趣,請隨時與我們聯絡。