研究計劃3 - 大規模人工智能硬件的電子設計自動化(EDA)

探索人工智能晶片與系統設計EDA的新前沿,聚焦於支持小晶片(Chiplet)及3DIC設計,突破現有EDA工具的技術瓶頸及開發基礎AI模型在各種設計任務中的應用,以實現更靈活的晶片設計。

研究項目3-1:

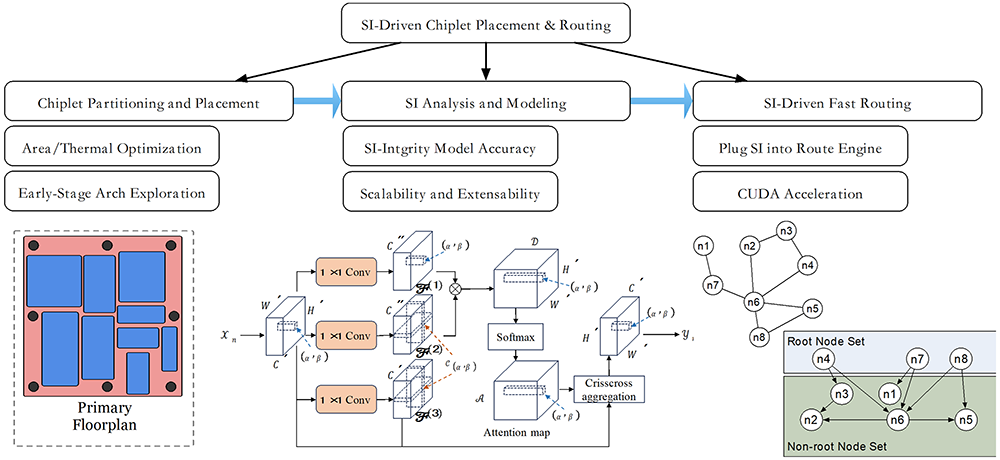

面向小晶片(Chiplet)的人工智能晶片訊號完整性驅動的電子設計自動化

研究項目3-1旨在研發面向基於Chiplet(2.5D 封裝)設計的自動化(EDA)解決方案,特別優化大規模 Chiplet設計中的訊號完整性(Signal Integrity, SI)問題。本計畫將首先支援 Chiplet的自動化分割與佈局規劃,綜合優化晶片面積、功耗等多重設計目標;同時,透過深入研究矽基板的互連結構與拓撲特性,建立具備可擴展性與高效率的訊號完整性分析方法。在此基礎上,開發一套以訊號完整性驅動的快速佈線優化工具。

研究項目3-2:

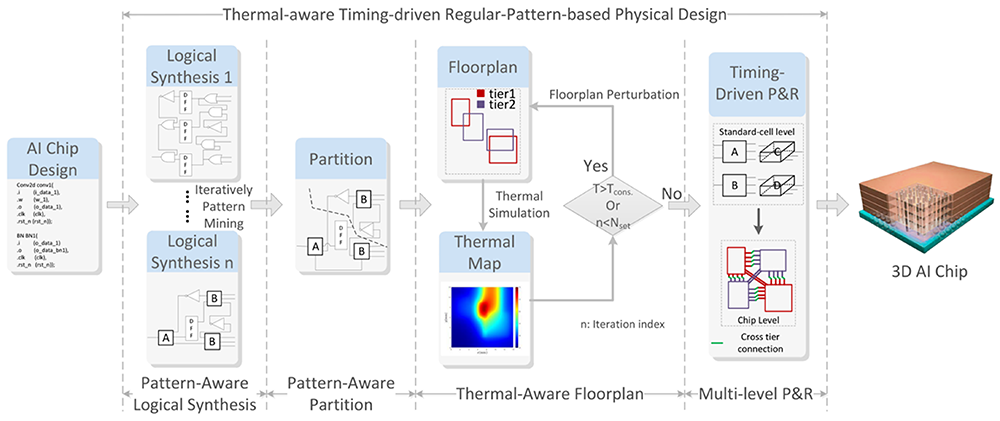

面向模式感知和熱感知的3D人工智能晶片電子設計自動化

研究項目3-2將進一步支援基於3D積體電路(3D IC)架構的人工智能晶片設計。該技術透過矽通孔(TSV)實現多個小晶片(Chiplet)的垂直堆疊,顯著提升記憶體頻寬與系統整合度。本研究提出針對 3D IC 導向的模式感知與熱感知電子設計自動化(EDA)解決方案,研究團隊將運用人工智能晶片中處理單元(Processing Element, PE)的規則性特徵,加速整體 3D 人工智能晶片的物理設計流程。此外,計畫將開發專用的熱模擬器,以實現晶片堆疊式 3D IC 的快速且精準的熱力分析;並在此基礎上構建具備熱感知能力的3D佈局規劃工具,以優化 3D IC 的設計與執行效率。

研究項目3-3:

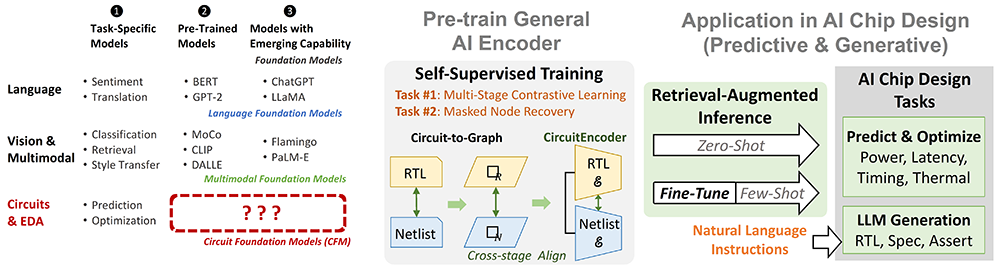

基於AI基礎模型的人工智能晶片靈活設計方法

研究項目3-3旨在基於客製化的 AI 基礎模型,開發先進的人工智能輔助電子設計自動化(EDA)技術。研究團隊將預先訓練通用電路編碼器,以生成每個電路元件的表徵。此通用電路表徵方法可實現從 RTL 階段到佈局階段的跨層設計一致性,並支持多種差異化的下游應用場景。基於涵蓋豐富電路資訊的特徵表示,計畫將構建各種人工智能模型,用於對延遲、時序與能效等關鍵設計指標進行早期、快速且精細的評估。此外,計畫亦將開發生成式人工智能模型,以輔助人工智能晶片的靈活自動化設計與優化。