研究计划1 - AI大模型的存内计算架构设计

解决计算、存储及存储带宽的扩展问题,尤其专注于推进基于存內计算(CIM)的芯片架构,以实现AI大模型的超高能效及可扩展部署。

研究项目1-1:

面向大语言模型应用的ReRAM-SRAM混合架构存内计算的人工智能处理器

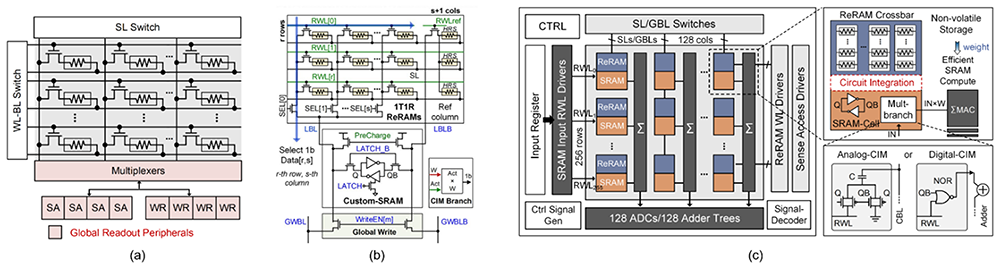

研究项目1-1旨在设计一款混合式存内计算(CIM)人工智能处理器,结合ReRAM与SRAM两种技术的优势。 ReRAM具备非易失和小体积等优点,但面对转换成本高昂与电阻变异等挑战;SRAM技术成熟且可靠,但占用面积较大且需大量数据传输。透过将ReRAM与SRAM整合至单一计算存储单元,本项目致力开发高性能、高效率的处理器,以支援AI大模型推理。此混合设计将包含晶体管级电路设计、分层分段式阵列结构,以及整体芯片存储系统,在确保MAC的可靠性和准确性的同时,显著改善延迟与降低能耗。

研究项目1-2:

基于存内计算技术的个人化大语言模型设备研究

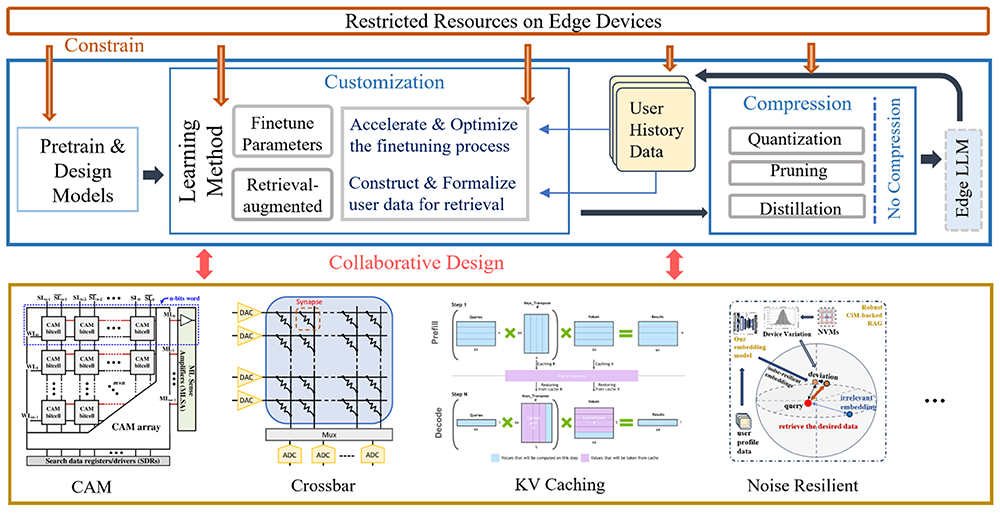

研究项目1-2透过采用存内计算(CIM)技术,实现具个人化功能的设备,以解决中心式云端大语言模型(LLM)与多模态大语言模型(LVLM)涉及的私隐与信任问题。研究团队将这些模型部署于边缘设备,既能提供个人化响应,同时确保相关数据保留于装置内。项目将探索模型压缩、量化及数据筛选等技术,使大模型能适应边缘设备计算环境。此外,研究将重点优化模型加速技术,以減少延迟与训练成本。透过开发数据精炼方法与自主学习框架,旨在提升边缘模型的个人化效能,为未来发展制定技术指南。

研究项目1-3:

基于3D非易失存储技术的可重构存内计算架构

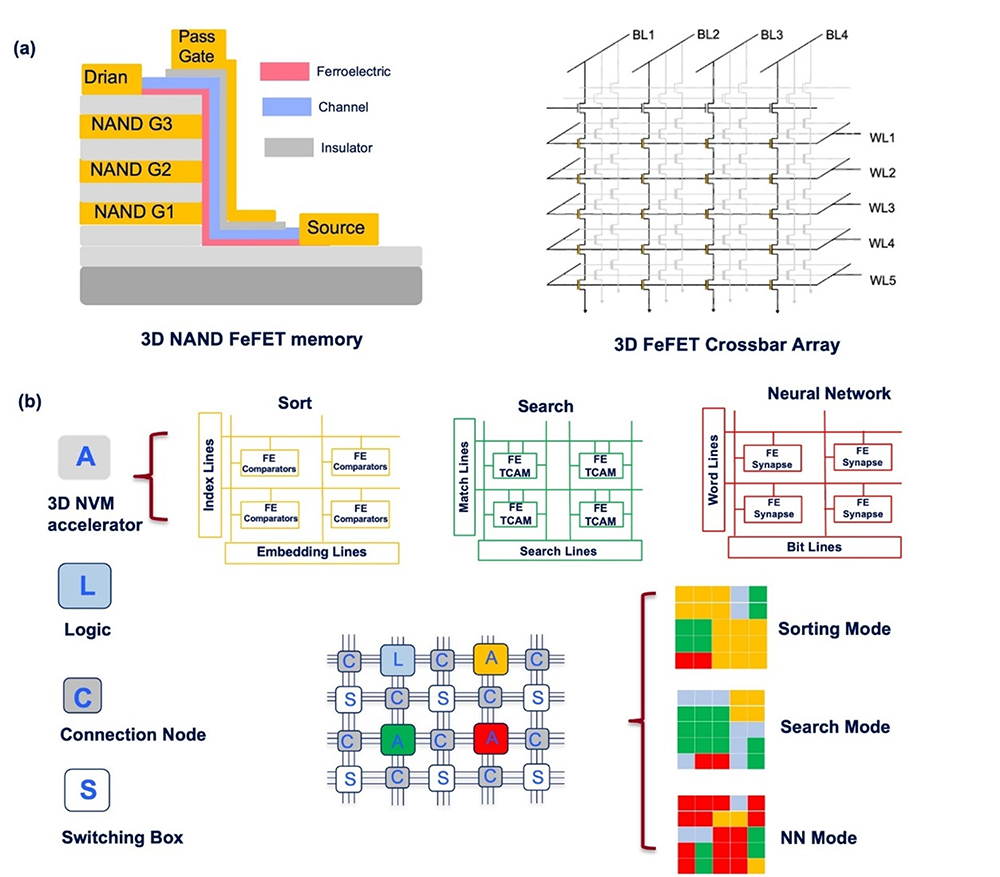

研究项目1-3旨在利用铁电存储(Ferroelectric Memory)等3D非易失存储(NVM)技术,开发可重构存内计算(CIM)架构,以突破现有CIM芯片的技术瓶颈。此类技术具备更高存储带宽、更低电压、更快写入速度及更为耐用,能显著提升CIM效能与效率。项目将利用NVM核心单元的重构与动态互连技术,构建可支援并行搜索、矩阵乘法等多种数据计算的可重构CIM架构。此方案预计能加速各类人工智能计算任务,彻底发挥CIM技术的应用潜能。

研究项目1-4:

面向AI大模型的以存储为中心的异构处理器

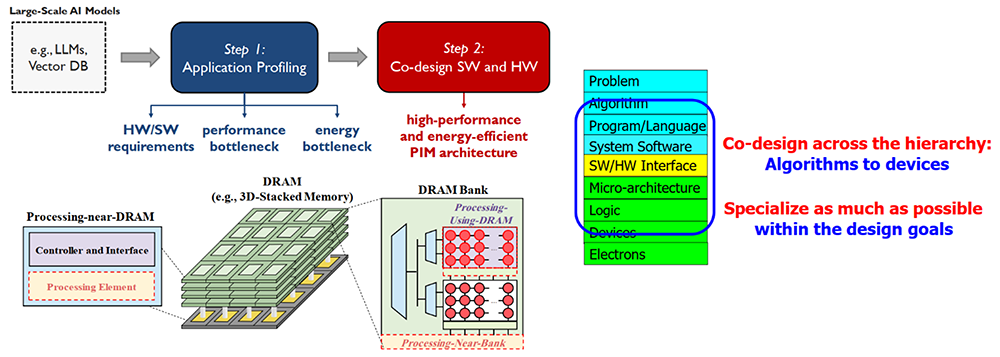

研究项目1-4针对限制当代计算系统效能与效率的数据传输瓶颈,设计由「以处理器为中心」转向「以数据为中心」,将处理单元贴近数据存储位置,探索近数据处理(NDP)与存内计算(PIM)架构。该架构将结合近存计算(PnM)与用存计算(PuM)技术最大限度地提高效益,目标是显著加速AI大模型及其他数据密集型工作负载,提升系统效能、能耗效率与扩展性,并使各种程序编制员与系统设计师能轻松应用此技术。